Integrovaný obvod

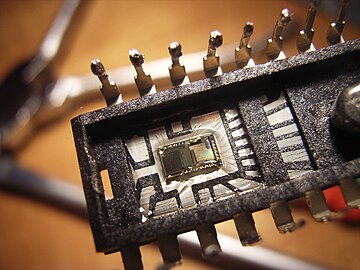

Integrovaný obvod , a integrovaný obvod ( anglicky integrovaný obvod , krátký IC , písmena jsou diskutovány: [ ʔiː ] [ TSE ] nebo zastaralé IS ) je velký na tenká, obvykle několik milimetrů plátek polovodičového materiálu uložen elektronický obvod . To je někdy označováno jako polovodičový obvod nebo monolitický obvod ( anglicky polovodičový obvod nebo monolitický integrovaný obvod nazýván). Tento čip ( anglicky The ) is usually to protect and simpler contact in a multiple larger chip package encapsulated. Integrovaný obvod typicky obsahuje kombinaci mnoha elektricky připojených elektronických polovodičových součástí, jako jsou tranzistory , diody a / nebo jiné aktivní a pasivní součásti .

Integrované obvody dnes mohou zahrnovat obvody s mnoha miliardami elektronických součástek (zejména tranzistorů), takže na polovodičové destičky o velikosti několika čtverečních milimetrů lze umístit i velmi složité obvody, jako jsou mikroprocesory a paměťové čipy. Mikrostruktury těchto prvků se od počátku 90. let vyráběly v rozsahu nanometrů . Obdélníkové polovodičové čipy jsou čipy (nazývané také již v zeleném stavu), zejména společně s aplikovaným elektronickým obvodem také mikročip . Integrované obvody se vyrábějí v našich vlastních továrnách na výrobu polovodičů v absolutně bezprašných čistých prostorách a zahrnují velké množství procesních kroků fyzikální a chemické povahy. Protože výkon mikroprocesorů a paměťových čipů obecně roste, jak se struktury na čipu zmenšují, jejich miniaturizace je často na hranici toho, co je technicky a fyzicky proveditelné. Existuje však také mnoho, zejména standardizovaných integrovaných obvodů, jako jsou logické moduly a operační zesilovače , kde to hraje jen malou roli - logické čipy široce používané řady 74xx , které se vyrábějí od 70. let, obsahují pouze řadu tranzistorů v jedno nebo dvouciferném rozsahu .

Používání jazyka

Hovorově se mikročip nebo čip částečně s IC srovnávat, i přesto, že čip je jen „vnitřní fungování“ z obvodu, to je, anglicky jako v určeném polovodičového čipu ke skutečné obvodu na něm.

Integrované obvody jsou také dvojité, trojité nebo jiné vícenásobné komponenty (bez ohledu na to, zda jako polovodičová součástka nebo trubice), které jsou každý ve společném krytu nebo ve skleněných žárovkách, jako jsou dvojité diody , triody , pentody , dvojité nebo Jsou umístěny trojité Darlingtonovy tranzistory atd.

příběh

předchůdce

Před vývojem integrovaných obvodů existovaly aktivní elektronické součástky, které byly pevně zapojeny spolu s několika pasivními a dodávány v jednom krytu. Jedním příkladem byly elektronové a vakuové trubice 3NF a 2HF vyvinuté v polovině 20. let - první trojitá trubice , podobná pozdější dvojité triodě ECC83 . Na rozdíl od mladší elektronky měly obě elektronky 20. let dva nebo dva odpory a dva nebo jeden kondenzátor zabudované do vnitřku elektronky, stejně jako v IC . Výsledkem byly hotové rádiové obvody - 3NF jako základní obvod pro místní příjem a zesílení a 2HF kromě volitelného dálkového příjmu, kde musely být připojeny pouze externí komponenty pro výběr stanice , napájení a přehrávání ( reproduktory nebo sluchátka ) a anténa.

Na konci 50. let byly elektronické obvody konstruovány s diskrétními součástmi; H. s jednotlivými tranzistory , diodami atd., které byly spojeny na desce s plošnými spoji za účelem vytvoření obvodu, srov. Integrace (technologie) . Z hlediska velikosti a životnosti to byl již velký průlom ve srovnání s elektronkami, které v té době konkurovaly .

Ještě před vynálezem tranzistoru bylo elektronické součástky, že integrované několik funkcí v jedné součásti , ve formě multi-systém trubek , kompozitových trubek jako je 3NF , duo diody nebo více anodových usměrňovačů rtuťové , které fungují jako několik řízených nebo neřízených usměrňovačů v jedné složky (a katoda a několik anod) dohromady. Tranzistory mají rozhodující výhody oproti elektronkám, např. B. Nižší spotřeba energie a menší velikost. S využitím desek plošných spojů a výsledného zmenšování výrobků začala tato novější technologie nahrazovat dřívější integrované systémy založené na elektronkách. Tento trend se zcela zintenzívnil s vývojem a masivním využíváním integrovaných obvodů od 60. let.

Jacobi patent

Málo známý je „polovodičový zesilovač “, který vynalezl a patentoval Werner Jacobi v roce 1949 , obvod složený z pěti tranzistorů na polovodiči, který slouží jako nosný materiál. Ty tvoří třístupňový obvod zesilovače ve formě integrovaného obvodu. Dva tranzistory jsou přepínány „nad hlavou“ a ovlivňují tak převod impedance mezi fázemi tranzistoru. Jacobi uvedl, že například sluchadla mohou být malá, lehká a levná.

Okamžité komerční využití jeho patentu není známo. Formulace integračního konceptu je zveřejněna v aplikaci z 15. května 1952: „polovodičový zesilovač, který se vyznačuje tím, že na polovodičové součástce je umístěno množství působících v různých spínacích nebo zesilovacích fázích.“ To znamená například integraci více diod emitujících světlo do Základní myšlenka bydlení sahá až k Jacobi.

Od Kilbyho a Noyce po dnešek

První integrovaný obvod ( klopný obvod ) vyvinul Jack Kilby v září 1958 . Skládal se ze dvou bipolárních tranzistorů, které byly připojeny k germániovému substrátu a spojeny zlatými dráty. Tento hybridní obvod je tedy prvním příkladem implementace již známé tranzistor-tranzistorové logiky (TTL) v obvodu. Byla to přípravná fáze pro další vývoj obvodů TTL směrem k menším návrhům.

První „monolitický“, tj. H. V červenci 1959 požádal Robert Noyce o patent na integrovaný obvod vyrobený z nebo v jediném monokrystalickém substrátu . Rozhodujícím faktorem v Noyceově vynálezu byla úplná výroba komponentů, včetně kabeláže, na substrátu. K výrobě již byly použity fotolitografické a difúzní procesy, které společnost Fairchild Semiconductor nedávno vyvinula pro výrobu prvního moderního difuzního bipolárního tranzistoru. Na základě těchto technologií byly mimo jiné v letech 1970/71 představeny první mikroprocesory tří společností: Intel 4004 , Texas Instruments (TI) TMS 1000 a Garrett AiResearch „Central Air Data Computer“ (CADC).

První integrované obvody v sériové výrobě se objevily na počátku 60. let (zejména u společností Texas Instruments a Fairchild Semiconductor ). Skládaly se pouze z několika desítek bipolárních tranzistorů ( anglická integrace malého rozsahu , SSI), obvykle v technologii RTL . V průběhu let se však komponenty stále zmenšovaly, integrovaly se pasivní součásti, jako jsou rezistory, a zvýšila se složitost integrovaných obvodů. Tím se také zvýšil počet tranzistorů na čip nebo na jednotku plochy; počet tranzistorů byl nejdůležitější charakteristikou integrovaných obvodů.

Zbrojní průmysl a cestování do vesmíru byly stimulujícím faktorem pro další rozvoj. Do poloviny šedesátých let byla vláda USA hlavním kupujícím integrovaných obvodů. Cílem bylo miniaturizovat technologii v obou oblastech. Od roku 1965 byl program Gemini vybaven palubními počítači založenými na integrovaných obvodech.

Při integraci ve středním měřítku (MSI) byl prostor pro několik stovek tranzistorů, u integrace ve velkém měřítku (LSI) na začátku 70. let pro několik tisíc tranzistorů. To umožnilo poprvé integrovat celý hlavní procesor (CPU) jako takzvaný mikroprocesor na čip, což výrazně snížilo náklady na počítače . Na začátku 80. let 20. století následovala velmi rozsáhlá integrace ( VLSI ) s několika stovkami tisíc tranzistorů, pomocí nichž bylo možné brzy vyrobit paměťové čipy ( RAM ) s kapacitou 256 KiBit a 1 MiBit. S tímto dalším vývojem výrobní technologie šla ruku v ruce rostoucí stupeň automatizace návrhu (viz návrh čipu ) designu a fotomasky potřebné pro výrobu, bez nichž již vývoj složitějších obvodů nebyl možný.

V roce 2010 obsahovaly grafické procesory až tři miliardy tranzistorů (viz Nvidia Tesla ), „běžné“ procesory pro všeobecné použití až 1,17 miliardy tranzistorů (Intel Core i7-980X). Itanium 2 Tukwila se skládá z 2,05 miliardy tranzistorů. Grafické procesory nyní dosáhly počtu tranzistorů přes osm miliard tranzistorů ( Nvidia GTX TitanX ). Ještě většího počtu je dosaženo s paměťovými moduly, ale s menší složitostí celého čipu.

Druhy a použití

přehled

Hlavním rysem integrovaných obvodů je velké množství různých nebo identických aktivních a pasivních součástí - mezi ně patří rezistory a kondenzátory - stejně jako spojovací vodivé dráhy na monokrystalickém substrátu nebo v něm . Tímto způsobem tvoří protějšek obvodů složených z jednotlivých (diskrétních) komponent pájených na desce s obvody . Tlusté a tenkovrstvé obvody - přičemž komponenty se vyrábějí depozicí par a strukturováním tenké vrstvy na skleněném substrátu - a ( hybridní obvody ) zaujímají mezilehlou polohu . Existuje celá řada dalších rozdílů:

Podle výrobní technologie

- monolitické obvody: všechny komponenty jsou vyráběny na jednom kusu (substrátu) monokrystalického polovodičového materiálu ( čipu ); Obvody se obvykle vyrábějí dopingem nebo epitaxí na povrchu podkladového materiálu (diody, tranzistory, až několik mikrometrů nad a pod původním povrchem) nebo nanášením vrstev (rezistory, vodivé stopy, kondenzátory, izolace, brány MOSFETů , epitaxe) .

- Tenkovrstvé obvody jsou součásti, které se vyrábějí depozicí par na skleněném substrátu. Většinou jde o odporové sítě. Mohou být také vyrobeny s nejvyšší přesností pomocí vyvážení elektronového paprsku . Jsou chráněny malbou dipem. Do této skupiny patří také obvody vyrobené z tenkovrstvých tranzistorů (TFT), jako jsou obvody používané např. B. najít aplikaci na plochých obrazovkách.

- Tlusté hybridní obvody kombinují několik monolitických čipů, stejně jako tištěné vodiče a pasivní součásti (téměř pouze rezistory) v technologii tlustých vrstev, většinou na keramickém substrátu; často jsou potaženy máčením.

Podle typu signálu

- Digitální integrované obvody zpracovávají nebo ukládají signály, které jsou k dispozici ve formě několika samostatných úrovní.

- Analogové (lineární) integrované obvody zpracovávají signály s jakýmikoli mezilehlými hodnotami.

- Integrované obvody se smíšeným signálem mají analogové i digitální obvody.

Integrované obvody senzorů a akčních členů jsou převaděče mezi různými fyzikálními veličinami, které se vyrábějí pomocí mikroelektronických technologií. Příkladem jsou integrované obvody v CMOS kamerách , mikrozrcadlové akční členy , Hallovy sondy , snímače zrychlení nebo obvody pro měření jejich teploty, osvětlení nebo pro příjem digitálních infračervených signálů

Po úkolu

- Procesory se používají jako výpočetní a řídicí jednotky pro počítače

- Polovodičové paměti ukládají digitální data

- Miniaturizované čipy v kontextu technologie RFID pro bezkontaktní identifikaci objektů a živých bytostí

- Standardní logické integrované obvody z různých logických rodin nabízejí funkce ve všech aplikacích

- ASIC jsou vývojově specifické aplikace (např. V toustovačích, ve vozidlech, v pračkách)

- ASSP jsou standardní produkty specifické pro aplikaci, které mají speciální aplikace podobné ASIC, ale jsou nabízeny výrobcem a nejsou vytvářeny na žádost zákazníka

- Integrované obvody senzorů převádějí a zpracovávají neelektrické veličiny (např. Zrychlení, světlo, magnetické pole)

- DSP (procesory digitálních signálů) zpracovávají digitální signály nebo analogové signály v digitální podobě

- Převodníky D / A a A / D převádějí digitální na analogové hodnoty nebo naopak

- FPGA ( Field Programmable Gate Array ) jsou digitální integrované obvody, které mohou být konfigurovány zákazníkem a skládají se z velkého počtu vzájemně propojitelných funkčních jednotek

- Mikrokontroléry (µC) obsahují všechny části malého počítače (programová paměť, aritmetická jednotka, hlavní paměť a registr)

- Výkonové integrované obvody mohou zpracovávat vysoké proudy a napětí (např. Jako úplné výkonové zesilovače nebo v napájecích zdrojích )

- Systém na čipu (SoC) jsou větší systémy kombinované na jednom čipu.

Výrobní

přehled

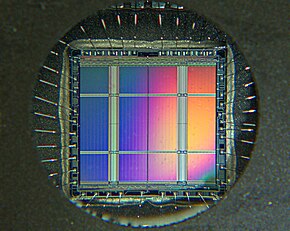

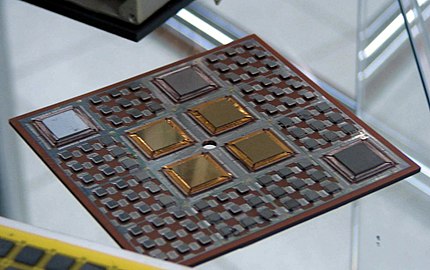

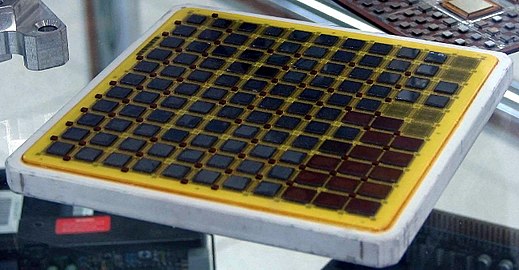

Integrované obvody jsou vyráběny výhradně na destičkách ( monokrystalická polovodičová destička), proto se hovoří o „monolitické výrobě“ nebo „monolitické integraci“. Na 300 mm desce mezi přibližně 80 (u velmi velkých procesorů obvykle s větší mezipamětí, např. Intel Tukwila ) a více než deseti tisíci (s jednotlivými tranzistory, jednoduchými obvody, LED diodami, fotodiodami atd.), Většinou identickými integrovanými Obvody vyráběné paralelně, což mimo jiné snižuje výrobní náklady. Kromě funkčních zkoušek lze výrobní proces rozdělit do tří základních částí:

- Výroba substrátů, která zahrnuje čištění výchozího materiálu, výrobu velkých monokrystalů (tzv. Ingoty ) a jednotlivých substrátů (destiček)

- Výroba jednotlivých komponent na oplatku, tzv. Front end . Tento krok lze rozdělit na:

- Front-end-of-line (. Anglicky front-end of line ., FEOL, dt, front-end of the production line '): (Aktivní) komponenty, jako jsou tranzistory, diody nebo kondenzátory, se vyrábějí zpracováním podkladového materiálu.

- Back-End-of-Line (angl. Back-end of line , BEOL, dt ,. Trailing end of the production line '): Tento krok zahrnuje v podstatě takzvanou metalizaci, kde jsou výrobky vyrobené v zařízeních FEOL navzájem spojeny a konečná pasivace povrchu.

- Rozdělení oplatek na jednotlivé čipy a jejich balení v pouzdrech, tzv. Back-end (nezaměňovat s back-end-of-line ).

„Hybridní integrace“ (hybridní technologie) - kombinace komponent z různých materiálů a výrobních procesů, jako je technologie tenkých a tlustých vrstev - jak se používá při výrobě mikrosystémů, dosud nebyla použita při výrobě integrovaných obvodů. Srovnatelná struktura, 3D integrace , ve které je několik čipů naskládaných na sebe a elektricky navzájem spojeny, by však mohla být použita v budoucích integrovaných obvodech, srov. Vícečipový modul .

Výroba substrátu

Základní materiál (substrát) obvykle slouží zároveň jako nosič a jako základní materiál pro aktivní oblasti diod a tranzistorů. Více než 99 procent integrovaných obvodů používá jako materiál substrátu křemík . Jiné materiály, jako je arsenid galia, se také používají pro velmi vysokofrekvenční nebo optické aplikace . Pro speciální aplikace se používají substráty křemík na izolátoru (substráty SOI) nebo křemík na izolačním substrátu, jako je safír ( silikon na safíru , SOS).

Aby bylo možné splnit vysoké požadavky mikroelektroniky, musí být substrát vyroben ve formě vysoce čistých monokrystalů . V případě křemíku je monokrystalický válec ( ingot ) nejprve odebrán z vysoce čisté křemíkové taveniny (srov. Extrakce čistého křemíku ). K tomuto účelu se primárně používá tzv. Czochralského metoda (CZ metoda). Alternativním postupem je zónové tavení , které lze také použít pro další čištění ingotů CZ; U některých speciálních aplikací je nutný vyšší stupeň čistoty než jeden cizí atom na 10 9 atomech ingotů CZ. Ingoty jsou nakrájeny na plátky tenké 0,5 až 1,5 mm, takzvané oplatky . Křemíkové destičky používané v hromadné výrobě dnes (2016) mají průměr 150, 200 nebo 300 mm (nazývané také 6, 8 nebo 12 palců), zatímco destičky o velikosti 450 mm jsou stále v úvodní fázi. Prostřednictvím různých procesů leptání, broušení a leštění získáte téměř dokonale rovný povrch s nerovnostmi řádově menšími než nanometr, tj. Jen několik atomových vrstev.

Přední část

Při výrobě integrovaných obvodů jsou všechny pracovní kroky před nakrájením plátku shrnuty pod pojem front-end ( tj. Přední / první část ). Probíhá v čistých místnostech s velmi nízkou hustotou prachových částic. To je nutné, protože i ty nejmenší částice (<0,1 µm ) mohou způsobit selhání celého obvodu. Použité procesy a postupy lze zhruba rozdělit do následujících skupin:

- Strukturovací procesy (zejména fotolitografie pro strukturování fotorezistních masek, které v následujících krocích pokrývají oblasti na oplatce, které nemají být ošetřeny (např. Dotovány)),

- Proces struktury vrstev ( epitaxe , naprašování , napařování , CVD atd.),

- Odstranění a čištění vrstvy procesu (procesy suchého a mokrého chemického leptání) a

- Proces změny vlastností materiálu (např. Pečení , doping , tvorba silicidu ).

Produkce front-end je rozdělena na dvě větší oblasti: front-end-of-line (FEoL) a back-end-of-line (BEoL). Liší se jak z hlediska funkčních prvků, které mají být vyrobeny, tak z hlediska výrobních procesů používaných v polovodičové technologii a materiálech.

Počínaje nestrukturovanou destičkou, front-of-line v podstatě zahrnuje všechny procesní kroky pro výrobu elektricky aktivních a pasivních součástí (tranzistory, kondenzátory a také rezistory). V back-end-of-line jsou však elektrická spojení mezi těmito součástmi provedena a teprve poté spojena s fungujícím elektronickým obvodem . V přeneseném smyslu jsou dráty, tj. Tenké elektrické vedení vyrobené z kovu, vyráběny a spojovány podle schématu zapojení. Proto se mluví o elektroinstalaci nebo pokovování.

Hrubá dělicí čára pro FEoL a BEoL je kontakt tranzistorových elektrod. Zde použité základní postupy do značné míry odpovídají postupům v BEoL. Jelikož se však v této kritické oblasti používají speciální techniky a opět různé materiály, nelze ji jednoznačně přiřadit k jedné z oblastí. Proto byl pro tuto produkční sekci zaveden pojem střední linie .

V následujícím jsou zjednodušeným způsobem popsány základní procesní sekvence pro výrobu moderních, takzvaných tranzistorů s efektem pole oxid kovu a polovodiče (MOSFET) ve větších integrovaných obvodech.

Front-end-of-line

Front-end výroba typického mikroprocesoru začíná výrobou izolačních oblastí mezi jednotlivými komponentami. Od konce 90. let se používá tato tzv. Z velké části izolace hrobu (Engl. Shallow trench isolation STI). Zde první velké závažné oblasti v substrátu (obvykle křemík) leptané . Tyto oblasti jsou definovány pomocí dříve fotolitograficky strukturované masky odporu, která chrání pozdější aktivní oblasti tranzistorů před leptáním. Po leptání jsou výkopy naplněny elektricky izolačním materiálem (obvykle oxidem křemičitým), obvykle pomocí procesů chemického nanášení par (CVD). Aby se zajistilo, že se nevytvoří žádné nevyplněné oblasti, ukládá se podstatně více dielektrického materiálu, než je nutné. Aby se znovu získal hladký povrch, přebytečný materiál se odstraní chemicko-mechanickým leštěním (CMP) a povrch destičky se vyrovná.

Nyní další výrobní fáze, výroba takzvaných „dřezů“ (v angličtině následuje jamky ) a příprava pozdějšího kanálu tranzistoru dopováním materiálu substrátu. Vnější elektrická vodivost substrátového materiálu se lokálně mění. Například dopováním běžně používaného p-vodivého křemíkového plátku (viz také Czochralského proces ) bórem vzniká n-vodivý žlab, ve kterém jsou tranzistory s efektem pole p-kanálu (FET), tj. Tranzistor, jehož funkce je založena na Vytváří se vytvoření elektricky p-vodivého kanálu. Doping je nezbytný, aby bylo možné vyrábět dvě různé varianty tranzistorů s efektem pole (n-kanálové a p-kanálové tranzistory) pro technologii CMOS, která se používá v integrovaných obvodech již několik desetiletí . Kromě toho pn křižovatky, které vznikají při výrobě vany, pomáhají elektricky oddělit různě dotované oblasti. Nejjednodušší variantou je již popsaný proces s jednou vanou (zde pro p-vanu). Pro určité požadavky se však používá také dvojitý (p- a n-jamkový proces ) nebo trojitý-jamkový proces . V dnešní době se samotný doping obvykle provádí pomocí iontové implantace po celém povrchu plátku. Z důvodu ochrany oblastí, které nemají být dotovány nebo mají být dotovány odlišně, jsou pokryty pomocí dříve fotolitograficky strukturované masky odolnosti. Jedná se jako obvykle o „strukturní úroveň“ mokrými chemickými procesy (např. Roztok Piranha ) a / nebo odstraněno plazmové spalování . Stejné procesy se také používají pro dopování kanálu tranzistoru. Na rozdíl od jamek se však doping zavádí těsně k povrchu. Nakonec obvykle dochází k teplotnímu procesu, který léčí defekty mřížky, ke kterým došlo během implantace iontů, a elektricky aktivuje doping jeho začleněním do krystalové mřížky substrátu.

Třetí fáze procesu se používá k vytvoření zásobníku vrstvy brány a strukturování brány. V případě obvyklého procesu CMOS v 90. a 90. letech 20. století s oxidem křemičitým jako hradlovým dielektrikem a polysilikonem jako hradlovou elektrodou je velmi tenký první (několik nanometrů tlustý) oxid hradla vyroben, často prostřednictvím „ Rapid Thermal Oxidation “ (RTO, dt. O rychlé tepelná oxidace ). Poté následuje celoplošné nanášení vrstvy vrstev z polykřemíku a tenké zapouzdřovací vrstvy z oxidu křemičitého. Tato vrstva oxidu je strukturována pomocí fotolitografie a leptání. Po odstranění masky fotorezistu slouží výsledná strukturovaná vrstva jako tvrdá maska pro strukturování hradla pomocí procesu anizotropního suchého leptání, reaktivního iontového leptání (RIE). Kromě izolace výkopu je strukturování brány jedním z nejnáročnějších procesů ve FEoL. Obzvláště fotolitografie pro definování hradlové elektrody je stále technickým limitem pro miniaturizaci ( planárních ) tranzistorů, zde jsou vysoce specializované procesy, jako je přijít. Ponorná litografie , redukce linií masky odporu izotropním suchým leptáním (Engl. Resist shrink a) Stále více se používá více struktur . Již zmíněný mezikrok je také (relativně jednoduchý) speciální proces, který je nezbytný, protože fotolitografie mimo jiné není schopna poskytnout dostatečně silné masky fotorezistu s nezbytným rozlišením, které by vydržely proces leptání.

Jednoduše řečeno, po struktuře brány následuje definice zdrojových a odtokových oblastí. V případě starších technologických uzlů (větších než 350 nm) to zahrnovalo pouze speciální dopování oblastí zdroje a odtoku. U dnes běžně používaných LDD-MOSFETů (LDD = slabě dopovaný odtok ) to však zahrnuje dopování prodloužení odtoku ( prodlužovací implantát ) a halo implantátů, jakož i výrobu jednoho nebo více distančních prvků (německy: „spacers“) ), pomocí kterého lze relativně snadno ovládat polohu dopantů zavedených iontovou implantací. Teprve na konci následuje finální doping zdrojových a odtokových oblastí, kterým končí vlastní výrobní úsek FEOL. Nyní začíná kontaktování a propojování tranzistorů.

Middle-of-line

Po vlastní výrobě tranzistoru jsou jednotlivé komponenty připojeny. Než k tomu dojde, je však nejprve nutné elektricky kontaktovat tranzistorové elektrody. Sekce výroby kontaktů není jasně přiřazena k FEOL nebo BEOL, proto se tato sekce často označuje jako Middle-of-Line (MOL).

Aby se zajistil dobrý elektrický kontakt mezi polovodičovými oblastmi a kovovým spojením (viz Schottkyho kontakt ), jsou elektrody nejprve silikovány , například celoplošným nanesením niklové vrstvy a následnou tvorbou silicidu při vysokých teplotách. Po silicid tvorby, ukládání a planarization obvykle následuje mezilehlé dielektrické - obvykle nedotovaných sklo silikátové (Engl. Nedotovaných Silcat sklo nebo USG) s nízkou-K dielektrika (stále od poloviny-2000s). Následuje výroba kontaktních otvorů pomocí RIE a jejich vyplnění kovem, obvykle wolframem , který je nanesen pomocí CVD procesu a vyrovnán pomocí CMP.

Zátěžové vrstvy používané v některých tranzistorových technologiích, které jsou určeny k vyvíjení tlaku nebo napětí na tranzistorový kanál a mohou tak ovlivňovat pohyblivost nosiče náboje , se obvykle aplikují po vytvoření silicidu a přiřadí se k MoL.

Back-end-of-line

Skutečné BEOL nyní následuje po metalizaci, tj. Výrobě sítě vodivých drah, se kterými jsou jednotlivé komponenty spojeny. Typickými materiály jsou hliník a od konce 90. let často měď. Výroba vodivých drah je vysoce závislá na použitém kovu. Například v případě hliníku je kov nejprve nanesen na celý povrch a poté strukturován pomocí fotolitografie a procesu suchého leptání . Tato metoda není u mědi možná, protože neexistuje žádný proces suchého leptání mědi, při kterém by se vytvářely plynné reakční produkty. Od počátku roku 2000 však došlo k úspěšnému výzkumu strukturování mědi ve vysokém vakuu pomocí suchého leptání. Místo toho je v případě mědi nejdříve strukturována izolační vrstva nanesená po celém povrchu a poté je měď pokovena galvanickými procesy. Zde se používají dvě hlavní techniky: damascénský a duální damascenský proces . Liší se způsobem, jakým jsou elektrická připojení, zvaná VIA ( anglicky vertical interconnect access ), vytvářena mezi skutečnými úrovněmi vodivé dráhy (jednotlivě nebo společně s úrovněmi vodivé dráhy). VIA odpovídají pokoveným otvorům na vícevrstvých deskách s plošnými spoji . Na obrázku jsou to oranžové svislé struktury. V hotovém integrovaném obvodu je potom 13 až 15 takových úrovní pokovování nad sebou. Velikost struktury se postupně zvyšuje ve vyšších úrovních, například první dvě úrovně se vyrábějí v nejmenší možné velikosti struktury (1 ×) a poté následují dvě až pět úrovní s větším rozestupem struktury (např. 2 ×), což může být až 32- krát (32 ×) hrubší struktury pokračují v nejvyšší úrovni (střední úrovně lze vynechat).

Kromě těchto konvenčních pokovování existují i jiné techniky, jako je křemík via ( anglicky through-silicon via , TSV). V současné době se používá v některých aplikacích senzorů, které vyžadují určité funkce na přední i zadní straně čipů, například některé biosenzory. Je však také považována za slibnou technologii pro realizaci budoucí 3D integrace integrovaných obvodů. Několik (silně ztenčených) čipů je naskládáno na sebe a jednotlivé úrovně čipů jsou navzájem elektricky spojeny pomocí TSV. Vzhledem k tomu, že v obou případech jsou TSV přes oplatku, nazývá se také úroveň oplatky přes křemík přes (dt. Křemík přes oplatku ), viz také ITRS v roce 2009.

V případě některých komponent, jako je IGBT , je strana protilehlá k obvodu dodatečně metalizována, aby se vytvořil vodivý kontakt; avšak pouze s jednou nebo dvěma úrovněmi metalizace.

Zadní konec

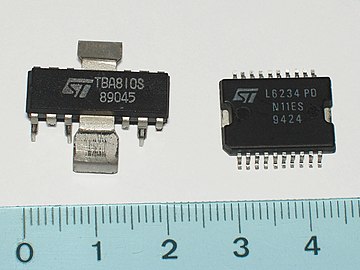

Pro použití na desce s plošnými spoji musí být citlivý čip zabudován do pouzdra .

V takzvané zadní části jsou destičky rozděleny na jednotlivé čipy a ty jsou obvykle umístěny v krytu.

Před nakrájením na kostičky jsou oplatky často ředěny broušením, které se označuje jako „backlapping“. Oplatky pak mají tloušťku pouze přibližně 100 až 200 µm. Ředění se provádí za účelem zlepšení chování chlazení čipu. To je možné, protože v integrovaných obvodech využívajících tenkovrstvou technologii jsou elektricky aktivní oblasti umístěny pouze v prvních mikrometrech na povrchu strany struktury. Zbývající podkladový materiál se používá pouze pro mechanickou stabilitu. U řezaných třísek již není nutná plná tloušťka substrátu. Silné podklady však mají vyšší tepelný odpor. Protože chladiče jsou obvykle připevněny k zadní straně podkladu, mají ztenčené destičky lepší chladicí vlastnosti.

Rozdělení oplatek na jednotlivce Toto se obvykle provádí řezáním, zřídka také bodováním a lámáním. Aby se raznice během řezání nerozpadly, je destička před řezáním nalepena na řezací fólii. Jelikož pila odstraňuje kousek z oplatky, třísky nejsou uspořádány plynule vedle sebe, ale mají mezi sebou určitou vzdálenost. V těchto stopách, tzv. „ Scratch frames “, se také používají testovací struktury, které se mimo jiné používají pro měření PCM bezprostředně po výrobě front-endu . Tyto zkušební struktury jsou při řezání zničeny.

V následném balení (angl. Packaging ) jsou potom jednotlivé integrované obvody zavedeny do pouzdra a kontaktovány, tzv. Lepením . V závislosti na typu se používají různé procesy, například lepení třísek nebo drátů . Uzávěr ( Einhausen ) se používá k hermetickému utěsnění proti vlivům prostředí - u čistě elektrických obvodů musí být pouzdro plynu a světlo těsné - a ke zlepšení použitelnosti. Buď jsou třískové a spojovací dráty uzavřeny v dutině (plech, keramika, případně s okénkem) nebo zapouzdřeny syntetickou pryskyřicí (lití, technika vstřikování ). Vysoce složité obvody (většinou pro mobilní aplikace) byly v poslední době (2009) použity také bez základního krytu a pájeny přímo na příslušné desky s obvody (srov. Ball Grid Array ). Nakonec je tu ještě jeden funkční test, ve kterém jsou ověřeny zaručené vlastnosti na všech obvodech. Typová zkouška se provádí náhodně nebo pouze ve fázi vývoje. Rutinní test se používá k třídění do obvodů různých kvalitativních tříd (například podle offsetového napětí v operačních zesilovačích ) a výsledky testu a typ omezení určují oblast použití. Tímto způsobem se vyrábějí vysoké kvality pro zvýšené provozní teploty a požadavky na prostředí (takzvaný standard MIL pro vojenské a vesmírné aplikace). U hromadných aplikací (spotřební zboží) jsou možné vyšší tolerance a plastové krytky.

V posledním kroku je pouzdro vytištěno s informacemi od výrobce, např. B. s názvem výrobce, číslem typu, datem výroby u. Na rozdíl od front-endové výroby dominuje u back-endové výroby mikromechanika a metody zpracování plastů ( vstřikování ).

Funkční testy a monitorování procesů

Aby bylo možné reagovat na výkyvy procesu v rané fázi, v případě potřeby opravit vadné procesy nebo dokonce odstranit oplatky nebo šarže z výroby, jsou stále nedokončené integrované obvody testovány po mnoha procesních krocích. V klientském rozhraní se většinou jedná o náhodné vzorky ve formě testu PCM ( monitorování řízení procesu ). Pro stanovení technologických parametrů se zkouška (např. Zkouška tloušťky vrstvy) obvykle provádí bezprostředně po příslušném procesu, zde je někdy důležité zaznamenat také příslušné systémy, protože identické systémy se stejnými parametry vytvářejí odchylky, které mohou být mimo rozsah tolerance. Po rozhraní frontend jsou všechny integrované obvody před dalším zpracováním obvykle testovány na svou funkci. Nejdůležitější elektrické parametry použitých komponent jsou určeny na speciálních testovacích strukturách, které jsou umístěny ve škrábancích mezi čipy. Parametry musí vyhovovat určitým specifikacím, aby bylo zajištěno, že čipy budou spolehlivě fungovat v celém povoleném teplotním rozsahu a po celou stanovenou dobu životnosti. V některých případech lze určité funkce (vysokofrekvenční obvody nebo připojení čipu, které později nejsou připojeny k PIN) testovat pouze na matrici. Především z důvodu nákladů je třeba zabránit tomu, aby byly nefunkční integrované obvody dále zpracovávány v následném výrobním procesu.

Ačkoli tato měření probíhají plně automaticky na speciálních testovacích systémech ( Automatic Test Equipment ), náklady spojené s vysoce integrovanými procesorovými čipy téměř dosáhly výrobních nákladů. To je způsobeno hlavně skutečností, že úspory z rozsahu se během testování projeví pouze v omezené míře (například paralelizace je možná pouze u čistých digitálních obvodů) a novější integrované obvody obsahují stále více funkcí, které je třeba testovat jeden po druhém. Aby bylo možné rozlišit jemné struktury mikroelektroniky, dnes se používají pevné jehlové adaptéry , s nimiž lze rozlišit vzdálenost měřicího bodu 150 um. Díky přesnému vedení tuhých jehel lze pomocí těchto adaptérů zachytit a zkontrolovat kontaktní body o průměru 70 µm. Adaptér s tuhou jehlou také umožňuje kontakt s jemnými pólovými mikro-zástrčkami, které se dnes v mikroelektronice stále více používají. To znamená, že tyto zátky již nemusí být v kontaktu s rychle opotřebovaným spojovacím konektorem. Učící se křivka prochází všemi novými technologiemi FE. A. lze měřit výtěžkem funkčních stavebních bloků. Jelikož nová technologie FE vyžaduje značné náklady na vývoj (někdy i třímístné milionové částky), mají společnosti ekonomické výhody, které dosahují vysokých hodnot výnosů co nejrychleji.

Nakonec je zabalený čip před dodáním také podroben závěrečnému testu, aby bylo možné identifikovat chyby v produkci typu back-end. Testují se také některé vlastnosti, které se mění kvůli obalu nebo jejichž měření není možné bez pouzdra, například: B. vazba nebo určité vysokofrekvenční vlastnosti. Zabalený čip pak může přejít na sestavu desky plošných spojů.

Miniaturizace

Integrované obvody jsou považovány za samostatnou elektronickou součástku. Velikost IC substrátu (anglicky což ) je zpravidla jen několik čtverečních milimetrů a je výrazně menší než okolní bydlení, které jsou skutečné elektrické spoje (kolíky) na zvládnutelnou velikost pro pájení drží. Aby byly výrobní náklady často složitých a nákladných integrovaných obvodů co nejnižší, vyrábí se několik (sto až tisíc) integrovaných obvodů paralelně na takzvaných destičkách v mikroelektronice , ale výrobní tolerance a chyby, které se vyskytnou, brání stoprocentnímu výtěžku.

Aby se výrobní náklady udržovaly co nejkonstantnější nebo je dokonce snížily v následujících generacích složitějších integrovaných obvodů, zavádějí se v mikroelektronice dva hlavní trendy. Na jedné straně je plocha čipu pro jednotlivé integrované obvody udržována co nejmenší (hlavní trend), na druhé straně je co nejvíce integrovaných obvodů uloženo na destičce, zatímco pouzdro zohledňuje další požadavky (technologie pájení, odvod tepla atd.) A v závislosti na požadavcích trhu vykazuje také různé vlastnosti .

Udržování oblasti čipu pokud možno konstantní vede ke stále složitějším obvodům - moderním integrovaným obvodům. B. paměťové moduly a mikroprocesory mohou obsahovat miliardy komponent (zejména tranzistorů) - že jednotlivé komponenty, jako jsou tranzistory, musí být zmenšeny, což také umožňuje vyšší taktovací frekvenci a snížené provozní napětí, a tedy i spotřebu energie. Při konstantní ploše čipu však lze těžko ušetřit náklady díky vyšší paralelnosti ve výrobě. Proto byla standardní velikost oplatky ve výrobě zvýšena z 2palcových destiček na dnešní 12palcové destičky (skutečný průměr 300 mm). S rostoucí velikostí oplatky šlo ruku v ruce efektivnější využívání povrchu oplatky (méně odpadu). Aby se však kvalita výroby nejen udržovala na stejné úrovni, ale aby se zlepšila - což bylo kvůli malým komponentům nutné -, bylo nutné překonat hlavní výzvy v technologii potahování.

Obecně miniaturizace obvodů dosáhne následujících cílů:

- Jedním z cílů je efektivnější výroba, čehož je dosaženo mimo jiné paralelní výrobou na substrátu (anglicky wafer ) a tím i úsporou surovin při výrobě a dalším zpracování.

- Kromě toho by se komponenty měly stát efektivnějšími v provozu, takže redukce struktur umožňuje zvýšení spínacích rychlostí; toho se dosahuje například kratšími délkami vedení a tím kratšími časy přenosu signálu a nižší dobou latence při opětovném načítání kapacit v komponentách a snížením spotřeby energie integrovaných obvodů.

- Díky integraci dalších funkcí mohou nové integrované obvody často kombinovat funkčnost několika dříve diskrétních integrovaných obvodů, což může také zvýšit spolehlivost, což je důležitá výhoda oproti konvenčním pájeným obvodům, zejména v počáteční fázi integrovaných obvodů.

Tímto způsobem mají být vyráběny menší, energeticky úspornější komponenty s více a více funkcemi, což je zvláště důležité pro mobilní zařízení. Integrované obvody a jejich miniaturizace umožňují telefon , SIM , peněžní a kreditní karty, RFID , inteligentní senzory, menší a odolnější kardiostimulátory nebo sluchadla, MP3 přehrávače nebo kamery CMOS atd. A. v mobilních telefonech.

Oblasti použití

Integrované obvody dnes tvoří základ veškeré složité elektroniky, zejména výpočetní techniky. Pouze prostřednictvím integrace je možné na malém prostoru poskytnout rozsáhlé funkce. Integrované obvody navíc v mnoha případech umožňují technickou implementaci systémů, které by jinak byly příliš drahé, příliš složité, příliš silné, příliš velké nebo v zásadě neproveditelné.

Viz také

- Společné rozložení těžiště

- Integrovaná optika

- Stupeň integrace

- Mooreův zákon

- Robert Widlar , Gordon Moore , marcián Edward Hoff

- Vlastnické právo pro topografii polovodičů (v Rakousku)

webové odkazy

- Průkopníci ve vývoji IC na heise.de

- Datové listy pro různé mikročipy na datasheetcatalog.com (anglicky)

Individuální důkazy

- ^ Sborník trhlin (CP 2009) . University of Padua, Padua 2009, ISBN 978-88-95940-28-1 , s. 887.

- ^ Historie bezdrátových sítí . John Wiley & Sons, New Jersey 2006, ISBN 0-471-71814-9 , str. 339 a násl.

- ↑ Otto Stürner: Elektronová trubice. In: rádiová technologie. (= Göschenova sbírka. Svazek V). Verlag Walter de Gruyter, Berlín 1927, s. 68 a násl.

- ↑ Patent DE833366 : polovodičový zesilovač . Registrován 15. dubna 1949 , zveřejněn 30. června 1952 , přihlašovatel: SIEMENS AG, vynálezce: W. Jacobi.

- ^ A b Jack S. Kilby: Vynález integrovaného obvodu . In: IEEE Transaction on Electron Devices . páska 23 , č. 7 , 1976, s. 648-654 .

- ↑ Patent US2981877 : Polovodičové zařízení a struktura vedení. Podáno 30. července 1959 , publikováno 25. dubna 1961 , vynálezce: Robert N. Noyce.

- ↑ IM Ross: Vynález tranzistoru . In: Sborník IEEE . páska 86 , č. 1 , 1998, s. 7-28 .

- ^ RG Arns: Druhý tranzistor: raná historie tranzistoru s efektem pole oxid kovu-polovodičového pole . In: Engineering Science and Education Journal . páska 7 , č. 5 , 1998, str. 233-240 .

- ^ David C. Mowery, Nathan Rosenberg: Poválečná federální investice. In: Technologie a snaha o hospodářský růst. Cambridge University Press, Cambridge (Anglie) 1989, ISBN 0-521-38936-4 , str. 145 f.

- ^ Robert Slater: Zmenšení a zefektivnění počítače. In: Portréty v křemíku. Massachusetts Institute of Technology, Cambridge MA 1987, ISBN 0-262-69131-0 , s. 159.

- ↑ Nvidia: Špičková grafická karta GeForce GTX Titan X za 1000 $. In: heise online. Citováno 1. listopadu 2016 .

- ↑ V. Ney: leptání mědi a kobaltu působením chloru za sucha . Vyd.: Free University of Berlin, Department of Physics. Berlín květen 2004, s. 158 ( fu-berlin.de [PDF]).

- ^ Grafen. Komunita výroby a designu polovodičů, přístup do 10. února 2017 (americká angličtina).

- ↑ Úroveň plátku přes Silicon Via (TSV) pro 3D integraci . In: International Technology Roadmap for Semiconductors 2009 Edition. Montáž a balení . 2009, s. 18–19 ( itrs.net [PDF]). itrs.net ( Memento ze dne 9. října 2010 v internetovém archivu )